GENERATEUR HF (2MHz)

à synthèse de fréquence (Quartz - PLL - uP )

basé sur un Microcontroleur ATMEGA8

Je

vous ai déjà parlé ici de ces puissants microcontrôleurs RISC que sont les AVR

ATMEGA8-16.

Voici mon deuxième montage réalisé autour de l'un d'eux, afin de me familiariser avec le langage assembleur AVR ainsi qu'avec les diverses ressources de ces uP.

Moi qui connais bien les PIC, je n'ai eu aucune difficulté à migrer vers ces nouveaux circuits que je trouve plus

performants, mais dont l'architecture et les ressources restent assez semblables.

Vous trouverez dans le soft que je fournis:

- des routines permettant de piloter un afficheur LCD 1x16c ou 2x16c

- des routines d'affichage d'un octet ou d'un mot de 24 bits

- la mise en oeuvre de la division d'une fréquence (utilisation du Timer1 associé à l'entrée T1 et à la sortie OC1A sans génération d'interruption: le traitement est très rapide et ne consomme pas de temps processeur)

- une routine de MULTIPLICATION 8 bits x 16 bits résultat sur 24 bits (en complément de celle implantée dans la puce qui est de 8b*8b->16b)

- une routine de DIVISION 24 bits par 8 bits, résultat sur 24 bits

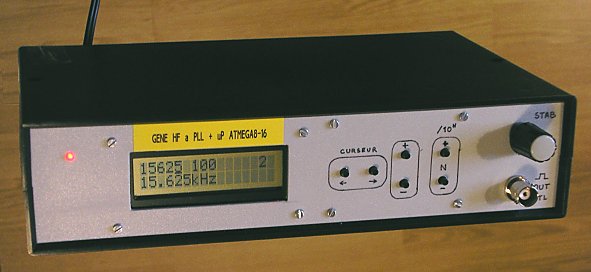

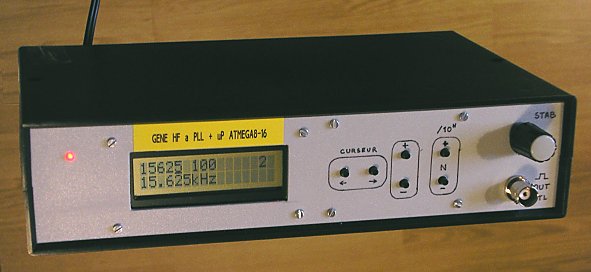

1 PRESENTATION

|

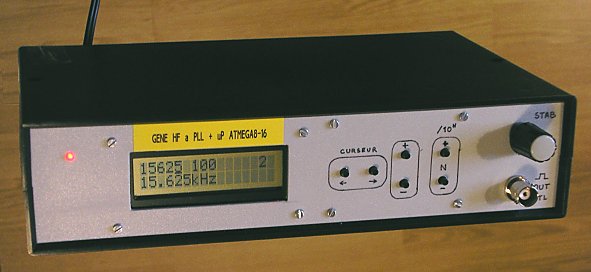

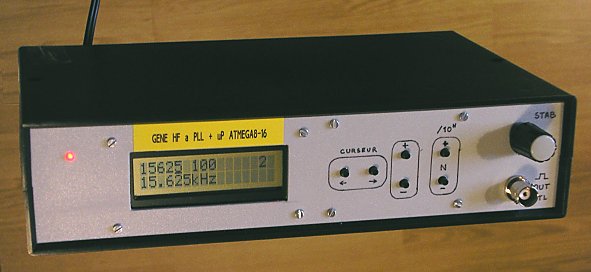

Voici le GENE HF sortant une

fréquence de 15625Hz (fréquence de balayage H TV)

Les petits points noirs sont des boutons poussoirs.

Les deux de gauche permettent de déplacer le curseur

(actuellement sous le chiffre 5)

Les deux suivants servent à incrémenter -

d'écrémenter le chiffre ainsi désigné.

Cette méthode de saisie a l'avantage par rapport à un

clavier numérique de pouvoir faire évoluer la

fréquence facilement par pas de 0.01Hz, ...., 1Hz, 10Hz, ...,

1000Hz... etc d'un simple clic sur un bouton.

Les deux de droite règlent le taux de division final par

puissance de dix (sept gammes : 1/1, 1/10, 1/100, 1/1000, 1/10 000,

1/100 000, 1/1 000 000)

Le GENE HF peut synthétiser 12.6 millions de fréquences

entre 0.20000 Hz et 2.0000 MHz

|

|

|

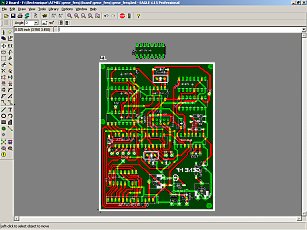

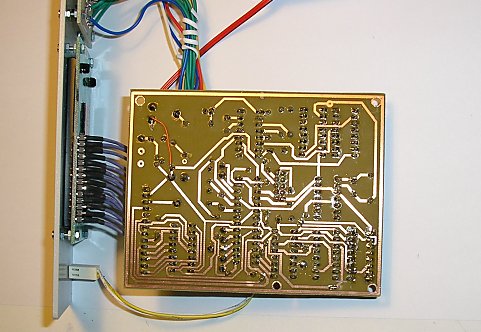

2 Le circuit imprimé

|

|

|

|

3 -

|

|

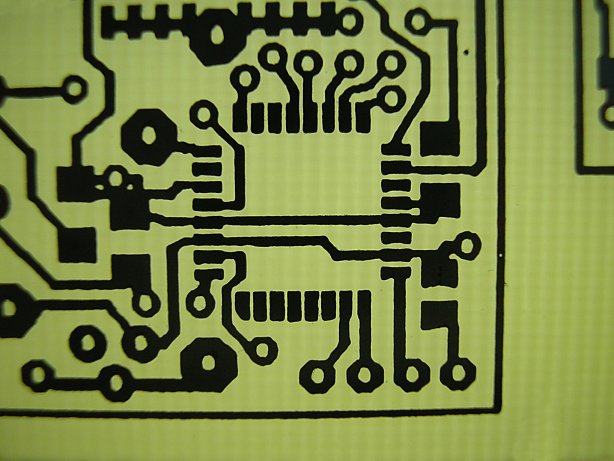

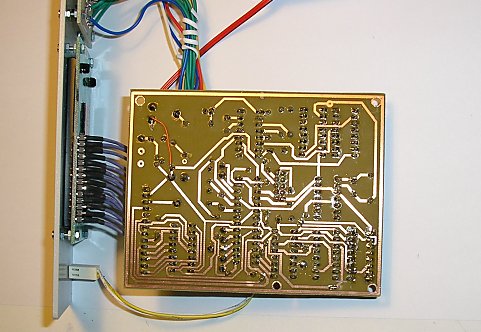

Le

circuit imprimé est

réalisé en double face avec toutes les pistes sur la face

'Bottom', la face 'TOP' (côté composants) servant de plan

de masse.

La réalisation est plus simple que celle d'un vrai double-face

puisqu'il n'y a qu'un typon a réaliser pour les pistes.

Coté plan de masse, il suffit d'éliminer le cuivre autour

de tous les trous avec un foret de 3mm avant de souder les composants

(sauf pour les pattes devant être reliées à la

masse, qu'on soudera directement sur le plan de cuivre).

Cette technique est bien connue de ceux qui font de la HF.

|

|

|

|

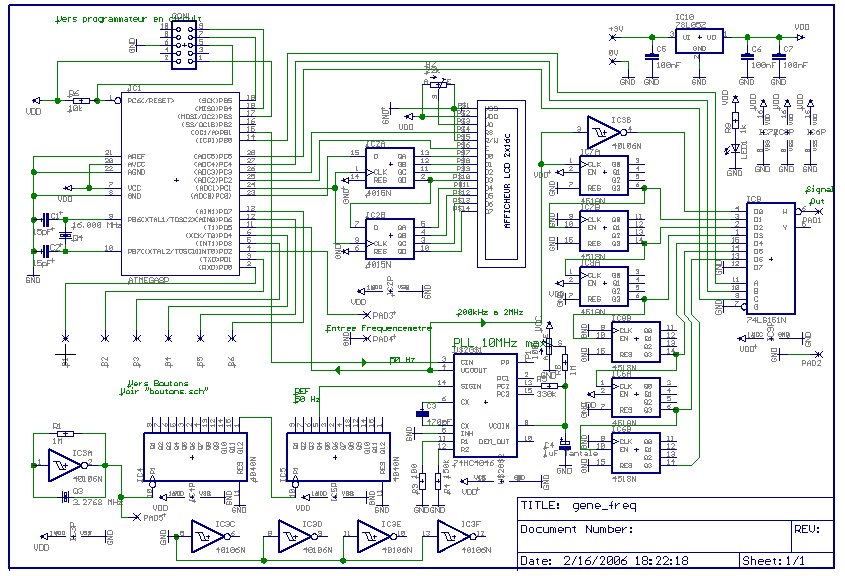

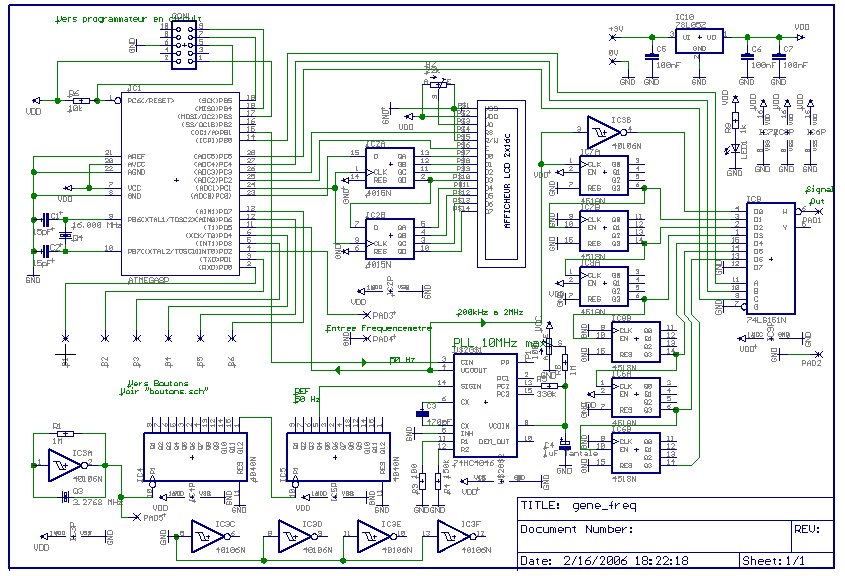

4 LE SCHEMA

|

|

|

|

5 PRINCIPE DE FONCTIONNEMENT

- Le VCO du 74HC4046 génere

une fréquence ajustable entre 200kHz et 2MHz. (Attention, la

version CMOS = CD4046 ne peut pas dépasser 1MHz).

- Cette fréquence est divisée par l'ATMEGA par

un nombre

à 5 chiffres (max 20 000) choisi par l'utilisateur afin

d'obtenir une fréquence de 50Hz.

- D'autre part une

fréquence de référence de 50Hz également,

est générée par division de la sortie d'un

oscillateur à quartz

(3.2768MHz = 100 x 2E15) par 2 x 10E15 (par les deux 4040 en bas sur le

schéma).

- Ces deux 50Hz sont soumis au comparateur de phase de

type II du 74HC4046 (voir son datasheet), le résultat (pin 13 du

74HC4046) est

intégré par une cellule RC (330k-1uF).

- La tension

d'erreur ainsi obtenue sert à asservir le VCO (pin 8 du

74HC4046).

Le pas minimum obtenu est de 100 Hz pour la gamme 2MHz, et il est bien

sûr divisé par le le même facteur que celui servant

à obtenir chacunes des autres gammes. Ainsi pour la gamme 20kHz,

il est de 1 Hz, et pour la gamme 2Hz il est de 0.1 milliHertz ! (A

comparer a certains appareils qui ont une résolution constante

de 1Hz par exemple, ce qui appréciable pour les

fréquences élevées, mais qui devient un peu...

juste pour les fréquence basses, lorsqu'il s'agit par exemple

d'une fréquence de sortie de 3Hz ajustable par pas minimum de

1Hz ! Je sais de quoi je parle, j'en ai acheté un !)

Le convertisseur N/A sert à stabiliser la phase du signal de

sortie (il permet de pratiquement annuler le bruit de phase, qui est le

point faible des systèmes à PLL, d'autant plus longues

à se stabiliser que la fréquence de

référence est basse. Mais une fréquence de

consigne basse permet un pas petit... ce qui est recherché ici).

Enfin un connecteur permet la programmation du microcontroleur in

circuit ( Voir ici ).

|

|

|

|

6 Documents techniques

|

|

|

|

|

7 EVOLUTION

21

février 2006:

Améliorations possibles:

- Utilisation d' un VCO montant à 90MHz (avec un 74F04 et

une varicap, puis division par un 74F161 j'y travaille, ça

fonctionne)

- Ou mieux, un VCO montant à 1GHz (oscillateur à

transistor BFR93A + varicap et division par un SDA2101)

20 mai 2006:

J'ai ajouté un

convertisseur N/A afin d'améliorer la vitesse et la

stabilité de l'asservissement de la fréquence.

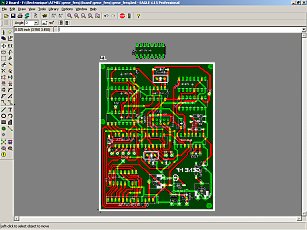

14 janvier 2008:

Le BRD dont je dispose n'est pas à jour par rapport au schéma, j'ai en

effet fait beaucoup de modifications après la réalisation du circuit

imprimé. Le schéma, lui, est à jour, mais je n'ai pas refait

l'implantation...

Si vous maîtrisez Eagle, le mieux est que vous routiez le schéma.

Pour info:Vous trouverez également sur ce site sur un géné piloté par uC ATMEGA programmé en PASCAL, avec un VCO 40

à 90MHz SINUSOIDAL (taux d'harmoniques très faible, controlé à

l'analyseur de spectre, amplitude asservie par diode PIN, fréquence par

varicap), affichage sur LCD bleu 4 lignes, etc...

|

|

|

|

|